kategorije: Izdvojeni članci » Praktična elektronika

Broj pregledavanja: 12919

Komentari na članak: 0

Chip 4046 (K564GG1) za uređaje s rezonantnim retencijom - načelo rada

Prilikom stvaranja energetskog elektroničkog uređaja s rezonancijskim zadržavanjem u krugu LC dizajniran je rezonantni krug regulatora za sinkronizaciju primljenih oscilacija s upravljačkim impulsima koji dolaze od pokretača.

Zadaća ovog regulatora je da zadrži rezonantne oscilacije u LC krugu pobudom u vremenu s njegovim vlastitim oscilacijama. Da bi se to postiglo, regulator mora primiti signal iz petlje iz kruga koji sadrži podatke o trenutnoj frekvenciji i fazi slobodnih oscilacija u njemu, nakon čega se, oslanjajući se na te podatke, održava stupanj pokretača u sinkronizaciji s tim frekvencijama i fazom, a zatim rezonanca u krugu će se automatski spremiti.

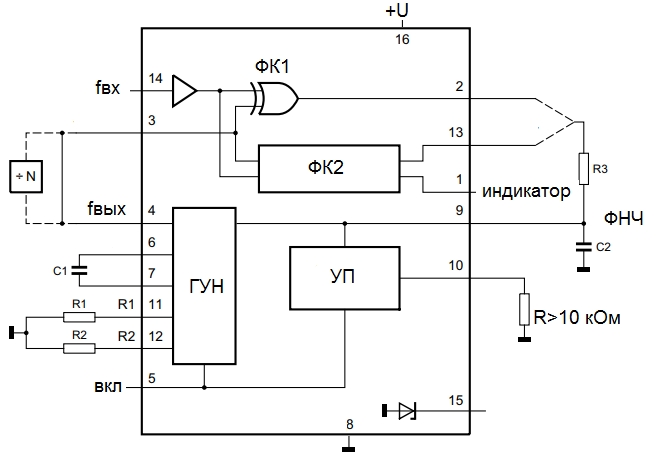

Za izradu takvog kontrolera pogodan je CD4046 čip ili njegov domaći kolega K564GG1. Pogledajmo uređaj ovog mikro kruga, svrhu njegovih zaključaka i shemu povezivanja montiranih komponenata, kako bismo shvatili, ako je potrebno, s čime se bavite.

Ovaj čip omogućuje vam da lako organizirate PLL - fazno zaključanu petlju. Za izgradnju PLL-a koriste se tri potrebna bloka koja se nalaze unutar mikro-sklopa: VCO - oscilator s nadziranim naponom, FC-fazni komparator i LPF - niskopropusni filter.

Ugrađen u mikro krug, VCO generira niz pravokutnih impulsa s 50% pokrivenosti, to jest čisti meander čija početna frekvencija ovisi o parametrima dva RC kruga: R1C1 i R2C2 spojeni na njega izvan mikrocirke, a amplituda je u ovom slučaju blizu napona napajanja mikro kruga. U +.

PLL princip rada

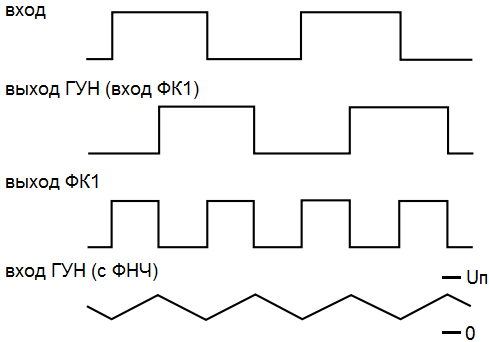

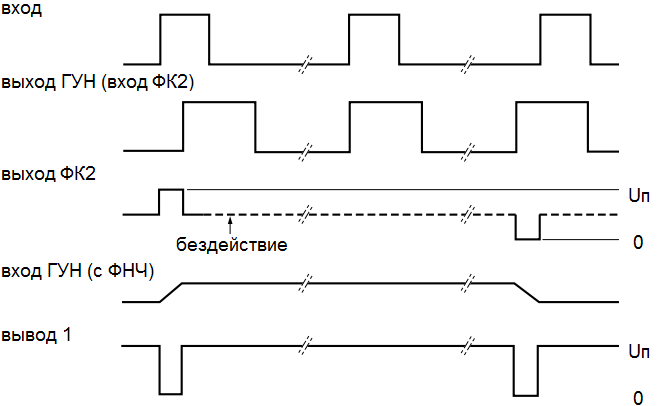

Vanjska ulazna signalna peraja dovodi se u mikro krug, zapravo na jedan od ulaza faznog komparatora FC (FC1 ili FC2 - odabere programer) unutar njega. Meander koji proizvodi VCO istovremeno se dovodi na drugi FC ulaz. Kao rezultat toga, na izlazu FC dobiva se pravokutni signal, čiji impuls ovisi o razlici između impulsa iz VCO i vanjskih impulsa u svakom trenutku.

U stvari, trajanje izlaznih impulsa s FC proporcionalno je faznoj razlici dva uspoređena signala. Činjenica je da se isključivi logički element često koristi kao FC, to znači da će na izlazu FC postojati visoka razina napona samo ako postoji razlika između signala, a ako nema razlike, tada će izlaz iz FC biti nizak razina napona ili neaktivno stanje.

Iz izlaza FC-a signal se dovodi do niskopropusnog filtra, što je jednostavan RC krug, na kondenzatoru kojeg se dobiva pulsirajući napon neusklađenosti, pri čemu je razina valovljenja proporcionalna razlici dvaju signala (od unutarnjeg VCO-a i dovodi se u mikrovezu izvana), ustvari - razlika faza ,

Napon neusklađenosti dobiven na LPF kondenzatoru odmah se vraća na ulaz VCO, a ovisno o njegovoj prosječnoj vrijednosti, VCO frekvencija će se automatski prilagoditi tako da se frekvencija meandra na njegovom izlaznom izlazu približi frekvenciji vanjskog signala koji dolazi s vanjske strane mikro kruga. Nakon postizanja ove situacije, prosječni napon na kondenzatoru niskopropusnog filtra bit će najmanji - to je znak početka maksimalne konvergencije dvaju signala u frekvenciji i fazi. Kad se signal uhvati, on će ga zadržati PLL petlja.

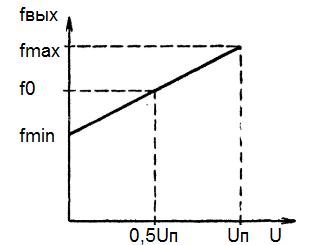

Granice reorganizacije VCO-a

Kao što ste već shvatili, VCO frekvencija se može prilagoditi unutar određenog raspona automatske prilagodbe. Ovaj raspon se postavlja vanjskim komponentama čipa. A brzina reakcije PLL sustava određena je vremenskom konstantom LFF (vrijednosti C2 i R3).Iz tog razloga treba strogo pristupiti izboru montiranih komponenti čipa.

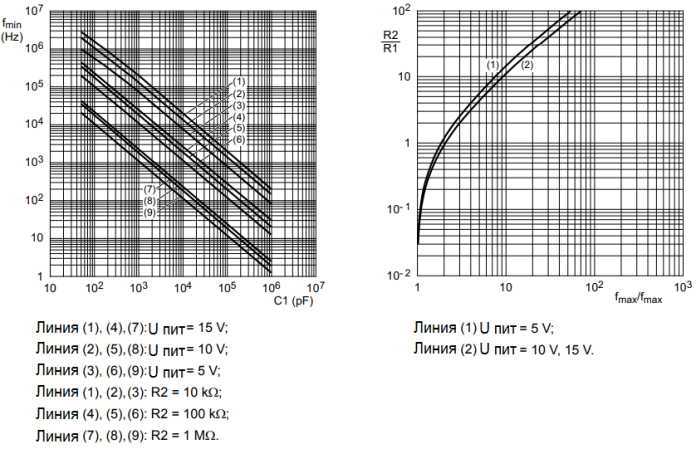

Napon napajanja mikro kruga, kondenzatora C1, kao i otpornici R1 i R2 određuju raspon samo-podešavanja VCO frekvencije unutar mikro kruga. Otpornik R2 pristrani minimalnu frekvenciju fmin VCO iznad nule. A omjer vrijednosti vrijednosti otpornika R1 i R2 određuje omjer između maksimalne i minimalne frekvencije - fmax / fmin, prilagodljiv izlazni signal iz VCO.

Ulazi i izlazi za čipove

Zaključak 4 - izlaz signala VCO, na njemu u radnom režimu meander. Ovaj se izlaz može koristiti za dovod signala u druge blokove dizajniranog uređaja.

Pin 5 odgovoran je za uključivanje i isključivanje VCO-a. Kad se napon visoke razine primijeni na ovaj izlaz, mikrovezje će se isključiti. Kada primjenjujete nisku razinu napona (kada spajate pin 5 na zajedničku žicu) - mikrovezje će raditi u normalnom načinu rada.

Zaključci 6 i 7. Kondenzator C1 povezan je s njima - ovo je kondenzator za podešavanje frekvencije VCO.

Zaključak 8 - zajednička snaga žice čipa.

Otpornik R1 je između stezaljke 11 i zajedničke žice. Otpornik R2 - između terminala 12 i zajedničke žice. To su otpornici na frekvenciju. Otpornik R3 niskopropusnog filtra - za pin 9 i pin 2 ili 13 (razlika između njih bit će razmatrana kasnije), kondenzator C2 niskopropusnog filtra nalazi se između pina 9 i zajedničke žice.

Pin 10 je izlaz pojačavača repetitora. Napon na njemu tijekom rada mikro kruga je napon neusklađenosti koji se dovodi do niskopropusnog filtra. Zaključak 10 osmišljen je tako da se napon neusklađenosti, ako je potrebno, lako izolira bez aktiviranja LPF kondenzatora. Do ovog zaključka dopušteno je spojiti otpornik s otporom većim od 10 kOhm.

Zaključak 15 - na njemu je katoda ugrađene zener diode sa stabilizacijskim naponom od 5,6 volta (stabilizacijski napon ove zener diode može biti različit, ovisno o proizvođaču čipa). Ova zener dioda opcionalno se može koristiti u strujnom krugu čipa.

Zaključak 16 - plus snaga čipa.

Ulazi i izlazi usporednika faza FC1 i FC2

Meander s izlaza VCO uzima se s terminala 4 i dovodi se u terminal 3, spojen preko pojačala-oblikovača na ulaze faznih komparatora FC1 i FC2. Po želji, signal iz VCO-a može se opcionalno proslijediti kroz djelitelj frekvencije.

Ulaz 14 je signalni ulaz i na njega se ulazi ulazni signal s kojim je potrebno sinkronizirati izlazni signal na izlazu VCO. Ovisno o prirodi ulaznog signala, programer može odabrati koji će fazni komparator koristiti: FC1 ili FC2, te na odabrani komparator priključiti niskopropusni otpornik filtra (na pin 2 ili 13). Fazni komparator FC2 ima indikator pin 1, na njemu se pojavljuje napon visoke razine kada su signali maksimalno sinkronizirani.

Osobitost FC1 je da je to jednostavan isključivi logički element ILI kvaliteta njegova rada ovisi o parametrima niskopropusnog filtra na njegovom izlazu. Rad započinje srednjom frekvencijom f0 = (fmax-fmin) / 2, moguće je uhvatiti harmonike središnje frekvencije. Ima visoku otpornost na buku.

Osobitost FC2 je da on obrađuje samo pozitivne razlike impulsa koji mu se isporučuju, pa stoga radni ciklus impulsa nije bitan. Rad započinje s minimalnom frekvencijom fmin, ne postoji mogućnost hvatanja harmonika središnje frekvencije. Ima nisku otpornost na buku. U filtru za niske propusne vrijednosti potreban je kondenzator s niskom propusnom strujom. FC2 je prikladniji za upotrebu u strujnim krugovima s LC rezonancom.

Odabir privitaka

Kao niskopropusni filtar ugrađeni su otpornik R3 i kondenzator C2. Da bi PLL ispravno radio, RC vremenska konstanta mora biti nekoliko desetaka puta veća od približne frekvencije hvatanja PLL-a.

U pravilu, programeru je otprilike poznata frekvencija hvatanja, pa ju oni u početku postavljaju rasponom automatske prilagodbe frekvencije: fmin i fmax. Prvi nomogram određuje, uzimajući u obzir napon mikrokruge i potrebni fmin, vrijednosti R2 i C1.Tada se prema drugom nomogramu, na temelju traženog omjera fmax / fmin, bira R1. Bolje je pružiti mogućnost podešavanja otpornika u krugu.

Pogledajte također na elektrohomepro.com

: