категории: Препоръчани статии » Практическа електроника

Брой преглеждания: 113767

Коментари към статията: 5

Интегриран таймер NE555 - история, дизайн и работа

Историята на създаването на много популярен чип и описание на неговата вътрешна структура

Една от легендите на електрониката е чип с интегрална схема NE555, Разработен е през 1972г. Такова дълголетие е далеч от всеки чип и дори не всеки транзистор може да се гордее. И така, какво е толкова специално в тази микросхема, която има три петици в своето маркиране?

Една от легендите на електрониката е чип с интегрална схема NE555, Разработен е през 1972г. Такова дълголетие е далеч от всеки чип и дори не всеки транзистор може да се гордее. И така, какво е толкова специално в тази микросхема, която има три петици в своето маркиране?

Signetics стартира серийно производство на чип NE555 точно една година след това тя е разработена от Ханс Р. Каменсинд, Най-удивителното в тази история беше, че по онова време Kamensind беше практически безработен: той напусна PR Mallory, но не успя да стигне до никъде. Всъщност това беше „домашна работа“.

Чипът видя светлината на деня и спечели толкова голяма слава и популярност благодарение на усилията на мениджъра на Signetics Art Fury, който, разбира се, беше приятел на Kamensind. Той работеше за General Electric, така че знаеше на пазара на електроника какво е необходимо там и как да привлече вниманието на потенциален купувач.

Според спомените на Каменсинда А. Фюри бил истински ентусиаст и любител на занаята си. Вкъщи имаше цяла лаборатория, пълна с радио компоненти, където провеждаше различни изследвания и експерименти. Това даде възможност за натрупване на богат практически опит и задълбочаване на теоретичните знания.

По това време продуктите на Signetics бяха наречени „5 **“ и опитният А. Фюри, който имаше свръхестествено усещане за пазара на електроника, реши, че маркирането на 555 (три петици) ще бъде най-добре дошло за новия чип. И той не се сбърка: микросхемата вървеше просто като горещи питки, стана може би най-масовата в историята на създаването на микросхеми. Най-интересното е, че микросхемата не е загубила своята актуалност и до днес.

Малко по-късно две марки се появяват в маркирането на микросхемата, тя става известна като NE555. Но тъй като в онези дни имаше пълна бъркотия в патентната система, интегрираният таймер се втурна да освободи всички, които не са мързеливи, естествено, поставяйки три (четете си) писма пред три петици. По-късно, въз основа на 555 таймера, двойни (IN556N) и четворни (IN558N) таймери са разработени, разбира се, в повече мулти-пинови случаи. Но основата все още беше същата NE555.

Фиг. 1. Интегриран таймер NE555

555 в СССР

Първото описание на 555 в домашната радиотехническа литература се появява още през 1975 г. в списание Electronics. Авторите на статията отбелязват факта, че този чип ще се радва на не по-малка популярност от широко известните по онова време операционни усилватели. И въобще не грешаха. Микросхемата направи възможно създаването на много прости дизайни и почти всички те започнаха да работят веднага, без болезнено регулиране. Но е известно, че повтаряемостта на дизайна у дома се увеличава пропорционално на квадрата на неговата "простота".

В Съветския съюз в края на 80-те години е разработен пълен аналог от 555 г., наречен KR1006VI1, Първото индустриално приложение на домашния аналог беше във видеорекордера VCR12 Electronics.

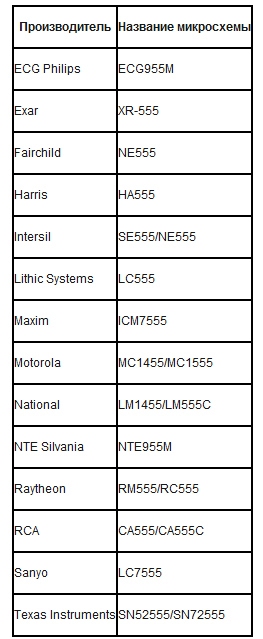

Производители на чипове NE555:

Чип за вътрешно устройство NE555

Преди да вземете поялника и да започнете сглобяването на конструкцията върху интегралния таймер, нека първо да разберем какво има вътре и как всичко работи. След това ще бъде много по-лесно да разберете как работи конкретна практическа схема.

Интегрираният таймер съдържа над двадесет транзисторивръзката на която е показана на фигурата - https://i.electricianexp.com/555ic.jpg

Както можете да видите, схемата е доста сложна и е дадена тук само за обща информация.В крайна сметка не можете да влезете в него с поялник, няма да можете да го поправите. В интерес на истината, това е точно това, което всички други микросхеми, както цифрови, така и аналогови, гледат отвътре (вижте - Легендарни аналогови чипове). Такава е технологията за производство на интегрални схеми. Също така няма да е възможно да се разбере логиката на устройството като цяло от такава схема, следователно функционалната схема е показана по-долу и е дадено нейното описание.

Технически данни

Но преди да се занимавате с логиката на чипа, вероятно трябва да донесете неговите електрически параметри. Обхватът на захранващите напрежения е достатъчно широк 4,5 ... 18V, а изходният ток може да достигне 200mA, което позволява използването на дори релета с ниска мощност като товар. Самият чип консумира много малко: само 3 ... 6 mA се добавят към тока на натоварване. В същото време точността на самия таймер практически не зависи от захранващото напрежение, - само 1 процент от изчислената стойност. Дрифтът е само 0,1% / волт. Температурният дрейф също е малък - само 0, 005% / ° C. Както можете да видите, всичко е доста стабилно.

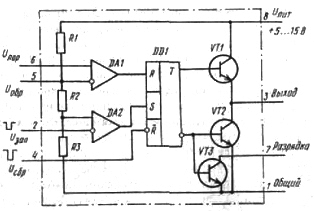

Функционална схема на NE555 (KR1006VI1)

Както бе споменато по-горе, в СССР направиха аналог на буржоазния NE555 и го нарекоха KR1006VI1. Аналогът се оказа много успешен, не по-лош от оригинала, така че можете да го използвате без страх или съмнение. Фигура 3 показва функционалната схема на интегрирания таймер KR1006VI1. Той е напълно съвместим с чипа NE555.

Фигура 3. Функционална схема на интегрирания таймер KR1006VI1

Самият чип не е толкова голям - той се предлага в осем пинов DIP8 пакет, както и в малък размер SOIC8. Последното предполага, че 555 може да се използва за редактиране на SMD, с други думи, разработчиците все още имат интерес към него.

В микросхемата има и малко елементи. Основното е най-често RS е спусък DD1. Когато логическа единица се подаде към вход R, спусъка се нулира на нула, а когато логически блок се подаде към вход S, той естествено се задава на единица. За генериране на управляващи сигнали на RS - входовете специална схема на компаратори, които ще бъдат обсъдени малко по-късно.

Физическите нива на логическа единица, разбира се, зависят от използваното захранващо напрежение и практически варират от Upit / 2 до почти пълния Upit. Приблизително същото съотношение се наблюдава за логически микросхеми на структурата на CMOS. Логическата нула е, както обикновено, в рамките на 0 ... 0.4V. Но тези нива са вътре в микросхемата, можете само да гадаете за тях, но не можете да ги почувствате с ръцете си, не можете да видите с очите си.

Изходен етап

За да увеличите товароносимостта на чипа, към изхода на спусъка е свързан мощен изходен етап на транзистори VT1, VT2.

Ако RS - тригерът е нулиран, изходът (пин 3) съдържа логическо нулево напрежение, т.е. отворен транзистор VT2. В случай, че спусъкът е инсталиран на изхода, нивото на логическата единица също е.

Изходният етап се осъществява от верига за издърпване, която ви позволява да свържете товара между изхода и общия проводник (клеми 3.1) или захранващата шина (клеми 3.8).

Малка забележка на изходния етап. При поправка и настройка на устройства на цифрови микросхеми един от методите за проверка на веригата е подаване на сигнал от ниско ниво към входовете и изходите на микросхемите. По правило това се прави чрез скъсяване до общата жица на тези входове и изходи с помощта на шевна игла, като същевременно не се причинява вреда на микросхемата.

В някои схеми захранването на NE555 е 5V, така че изглежда, че това също е цифрова логика и можете да го направите и доста свободно. Но в действителност това не е така. В случая на чипа 555, или по-скоро с неговия изход-издърпване, такива "експерименти" не могат да се правят: ако в този момент изходният транзистор VT1 е отворен, тогава ще се появи късо съединение и транзисторът просто ще изгори. И ако захранващото напрежение е близо до максимум, тогава плачевно приключване е просто неизбежно.

Допълнителен транзистор (щифт 7)

В допълнение към споменатите транзистори има и транзистор VT3. Колекторът на този транзистор е свързан към изхода на чипа 7 "Разряд". Неговата цел е да се разтовари кондензаторът за настройка на времето, когато се използва микросхемата като генератор на импулси. Разрязването на кондензатора възниква при нулиране на спусъка DD1. Ако си припомним описанието на спусъка, тогава на обратния изход (обозначен с кръг на диаграмата) в този момент има логическа единица, водеща до отварянето на транзистора VT3.

За сигнала за нулиране (пин 4)

Можете да нулирате спусъка по всяко време - сигналът за "нулиране" има висок приоритет. За целта има специален вход R (щифт 4), обозначен на фигурата като Usbr. Както може да се разбере от фигурата, нулиране ще се случи, ако към четвъртия изход се приложи импулс с ниско ниво от не повече от 0,7 V. В същото време на изхода на микросхемата ще се появи ниско напрежение (щифт 3).

В случаите, когато този вход не се използва, към него се прилага логическо ниво на единица, за да се отървете от импулсния шум. Най-лесният начин да направите това е като свържете щифт 4 директно към захранващата шина. В никакъв случай не трябва да го оставяте, както се казва, във „въздуха“. Тогава ще трябва да се чудите и мислите дълго време, и защо веригата работи толкова нестабилно?

Общи бележки за задействане

За да не се обърка напълно състоянието на спусъка, трябва да се припомни, че при дискусиите за спусъка винаги се взема предвид състоянието на неговия директен изход. Е, ако се каже, че тригерът е „инсталиран“, тогава на директния изход е състоянието на логическата единица. Ако кажат, че спусъкът е "нулиран", тогава директният изход със сигурност ще има състояние на логическа нула.

На обратния изход (маркиран с малък кръг) всичко ще е точно обратното, следователно често изходът на спусъка се нарича парафаза. За да не объркаме всичко отново, няма да говорим повече за това.

Всеки, който внимателно прочете до това място, може да попита: „Извинете, това е само спусък с мощна транзисторна каскада на изхода. И къде е самият таймер? “ И той ще бъде прав, защото въпросът все още не е достигнал таймера. За да получи таймер, баща му, създателят на Ханс Р. Каменсинд, измисли оригинален начин за управление на този спусък. Номерът на този метод е формирането на контролни сигнали.

Генериране на сигнал върху RS - входове на спусъка

И така, какво получихме? Спусъкът на DD1 контролира всичко вътре в таймера: ако е настроен на един, изходното напрежение е високо и ако е нулиран, тогава изходът 3 е нисък и транзисторът VT3 също е отворен. Целта на този транзистор е да разреди кондензатор за синхронизация във верига, например, импулсен генератор.

Спусъкът на DD1 се управлява с помощта на сравнителите DA1 и DA2. За да се контролира работата на спусъка на изходите на сравнителите, е необходимо да се получат сигнали от високо ниво R и S. Референтно напрежение се прилага към един от входовете на всеки сравнител, което се генерира от прецизен разделител на резистори R1 ... R3. Съпротивлението на резисторите е същото, така че напрежението, приложено към тях, е разделено на 3 равни части.

Генериране на сигнал за задействане на спусъка

Старт на таймера

Директното напрежение 1 / 3U се прилага към директния вход на компаратора DA2, а външното напрежение за стартиране на таймера Uzap през щифт 2 се прилага към обратния вход на компаратора. За да се действа на входа S на спусъка DD1 на изхода на този компаратор, е необходимо да се получи високо ниво. Това е възможно, ако напрежението Ustap ще бъде в диапазона 0 ... 1 / 3U.

Дори краткосрочният импулс на такова напрежение ще задейства спусъка DD1 и появата на таймер за високо напрежение. Ако входният Ucap е изложен на напрежение над 1 / 3U и до захранващото напрежение, тогава няма да има промени на изхода на микросхемата.

Спиране на таймера

За да спрете таймера, просто трябва да нулирате вътрешния тригер DD1 и за това на изхода на сравнителя DA1 генерирате сигнал от високо ниво R. Сравнителят DA1 е включен малко по-различно от DA2.Референтното напрежение от 2 / 3U се прилага към инвертиращия вход, а контролния сигнал "Праг на реакция" Ufor се прилага към директния вход.

С това включване, високо ниво на изхода на сравнителя DA1 ще възникне само когато напрежението Upoor на директния вход надвишава референтното напрежение 2 / 3U на обръщащото. В този случай спусъкът на DD1 ще бъде нулиран и на изхода на микросхемата ще бъде установен сигнал за ниско ниво (щифт 3). Също така транзисторът VT3 „разряд“ ще се отвори, който ще разреди кондензатора за настройка на времето.

Ако входното напрежение е в рамките на 1 / 3U ... 2 / 3U, нито един от сравнителите няма да работи, промяна в състоянието на изхода на таймера няма да се случи. В цифровата технология това напрежение се нарича „сиво ниво“. Ако просто свържете щифтове 2 и 6, ще получите сравнител с нивата на отговор 1 / 3U и 2 / 3U. И дори без нито един допълнителен детайл!

Промяна на еталонното напрежение

Заключение 5, обозначено като Uobr на фигурата, е проектирано да контролира референтното напрежение или неговите промени с помощта на допълнителни резистори. Възможно е също да се подаде управляващо напрежение към този вход, така че да е възможно да се получи честотно или фазово модулиран сигнал. Но по-често това заключение не се използва, а за да се намали влиянието на смущения, той е свързан с общ проводник чрез кондензатор с малък капацитет.

Микросхемата се захранва чрез щифтове 1 - GND, 2 + U.

Ето действителното описание на интегрирания таймер NE555. Таймерът е събрал много всякакви схеми, които ще бъдат разгледани в следващите статии.

Борис Аладишкин

Продължение на статията: 555 Интегрирани дизайни на таймерите

Вижте също на i.electricianexp.com

: