Kategorijos: Mikrovaldiklio grandinės

Peržiūrų skaičius: 21445

Straipsnio komentarai: 0

Kas yra FPGA paprasta kalba pradedantiesiems

Su kuo siejama skaitmeninė elektronika? Visų pirma, su loginiais elementais IR, ARBA, NE. Be to, į atmintį patenka poslinkių registrai, dekoderiai, multiplekseriai ir kt. Tačiau didėjant elektroninių prietaisų sudėtingumui ir miniatiūrizacijos tendencijai, iš minėtų komponentų sukurti įrenginius, paremtus integruotomis grandinėmis (IC), tapo sudėtinga, pritaikytos reikalingos topologijos ir schemų IC buvo vertos tik tada, kai įrenginys buvo dauginamas daug, kitais atvejais jis buvo nepagrįstai brangus.

Išeitis iš šios situacijos buvo programuojamų integruotų loginių schemų (sutrumpintai FPGA, užsienio santrumpa kaip programuojamas loginis įrenginys, PLD) kūrimas. Kas tai yra ir kur jis naudojamas, mes pasakysime šiame straipsnyje.

Skirtumai nuo mikrovaldiklių

Su žodžiu „programuojamas“ asocijuojasi dauguma pradedančiųjų su mikrovaldikliais. Nepaisant to, kad jie taip pat yra užprogramuoti, FPGA yra visiškai kitoks įrenginys.

Kūrėjams, turintiems mikrovaldiklius, yra fiksuotas sprendimų ir priemonių, būdingų tam tikrai mikroschemai, rinkinys, jis niekaip neveiks trauktis iš architektūros. Jums bus duotas komandų rinkinys, su kuriuo atliksite sąveikos su aplinka operacijas, skaitydami skaitmeninių ir analoginių įėjimų duomenis ir siųsdami signalus pavaroms naudodami išvestis.

Be to, galite atlikti skaičiavimus, išsaugoti duomenis registruose ar ROM, taip pat naudoti duomenis, įrašytus į mikrovaldiklio atmintį. Iš esmės tai yra darbo su mikrovaldikliais tikslas ir ypatybės.

Programuojamos loginės integruotos grandinės (FPGA) skiriasi tuo, kad programuodami įrenginį, jūs patys sukuriate architektūrą iš pagrindinių logikos elementų. Taigi, jūs gaunate didelį lusto greitį ir lankstumą. Tai suteikia galimybę nekeičiant vieno lusto įgyvendinti daugybę projektų.

Paprastai vidinį FPGA įrenginį galima suskirstyti į tris pagrindines grupes:

1. Loginių elementų (makro ląstelių, loginių blokų) masyvas.

2. Įvesties / išvesties blokai (IO).

3. Ryšio linijos tarp jų ir prietaiso, kuris valdo šias jungtis.

Tačiau toks struktūrizavimas yra labai apibendrintas, mes išsamiau apsvarstysime šią problemą toliau.

Programiuodami, elementus jungiate taip pat, kaip norėtumėte, surinkdami įrenginį iš atskirų elementų ir sujungdami jų įėjimus ir išėjimus su laidininkais.

Pastaba:

Pagrindinis skirtumas tarp FPGA ir mikrovaldiklių yra tas, kad mikrovaldiklyje negalima pakeisti vidinių jungčių tarp paprasčiausių elementų, o programavimas ir darbas su jais yra pagrįstas jungčių registravimu.

Mikrovaldikliai pasirenkami remiantis daugybe kriterijų, tokių kaip:

-

Greitis ir laikrodžio greitis;

-

ROM ir RAM kiekis;

-

Įėjimų ir išėjimų skaičius.

Kitos funkcinės savybės ir periferiniai įrenginiai, tokie kaip ryšių linijų ir protokolų palaikymas (I2C, vieno laido, PWM signalas ir kt.).

Renkantis FPGA, pagrindinis kriterijus yra programuojamų blokų skaičius - jų turėtų pakakti užduočiai įgyvendinti.

Priklausomai nuo konkretaus FPGA, blokų skaičius gali skirtis plačiomis ribomis ir atitinkamai kainuoti.

Mikrovaldiklis nuosekliai atlieka visas savo programoje nurodytas operacijas, o FPGA blokai užduotį atlieka lygiagrečiai ir nepriklausomai vienas nuo kito, todėl palyginti šiuos įrenginius pagal laikrodžio dažnį yra nepraktiška. Jų veikimo principas per daug skirtingas.

Rūšys

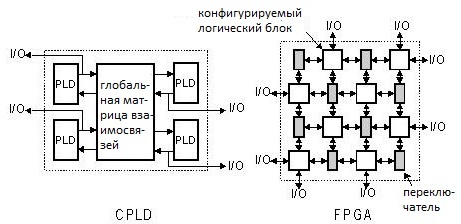

Šiuo metu svarbūs du pagrindiniai FPGA tipai:

1. CPLD (sudėtingas programuojamas loginis įrenginys - programuojamas loginis integruotas grandynas, iš tikrųjų tai klasikine prasme yra FPGA). Paprastai ji turi įmontuotą nekintamą atmintį, į kurią įkeliama programinė įranga.

Vidinė struktūra yra pastatyta ant makro ląstelių ar loginių blokų matricos, o jose esančių elementų skaičius yra šimtų ir tūkstančių vienetų diapazonas. Dėl santykinio paprastumo jie yra pigesni už kito tipo programuojamą logiką. Visa tai lemia, kad CPLD dažniausiai naudojamas tose schemose, kur reikalingas didelis greitis ir didelis išėjimų skaičius, atliekant paprastas užduotis.

2. FPGA (programuojamas lauko masyvas - vartotojo programuojamas vartų masyvas, tačiau jis dažnai vadinamas FPGA) - labiau išplėtoti ir sudėtingesni įrenginiai, palyginti su CPLD, yra sukurti ant loginių blokų su lanksčiu perjungimu ir juose yra daugiau elementų (dešimtys ar šimtai tūkstančių vienetų).

Programinė įranga paprastai laikoma išorinėje nekintamoje atmintyje. Be paprasčiausių loginių elementų, FPGA gali būti paruošti blokai, skirti atlikti bet kokias operacijas, pavyzdžiui, DSP signalo apdorojimo blokai. Visa tai leidžia įgyvendinti procesorių, signalo apdorojimo įrenginius ir kitus sudėtingus įrenginius.

Įdomu:

Nors iš tikrųjų nekintamos atminties buvimas nedaro programuojamo loginio CPLD. Tai iš dalies klaidina. Pagrindinis skirtumas tarp CPLD ir FPGA yra vidinė struktūra.

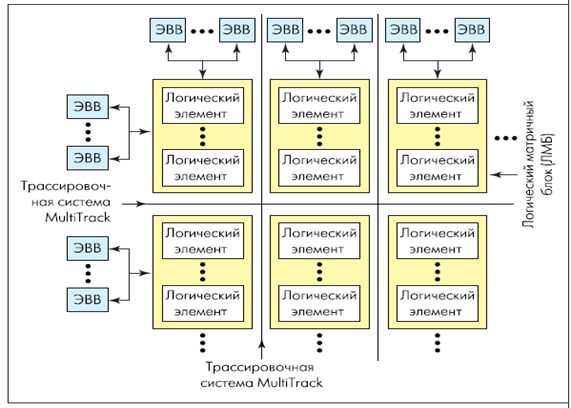

Vidinis CPLD įrenginys išsamiau parodytas paveikslėlyje žemiau.

Apytikslė jo makroelemento schema atrodo taip:

Makroelementą sudaro programuojami multiplekseriai, trigeriai (vienas ar daugiau) ir keliomis versijomis sudaro išvestinių FB signalų grupę.

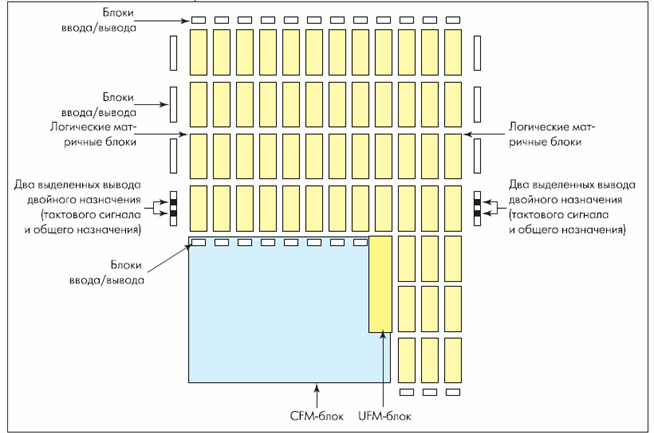

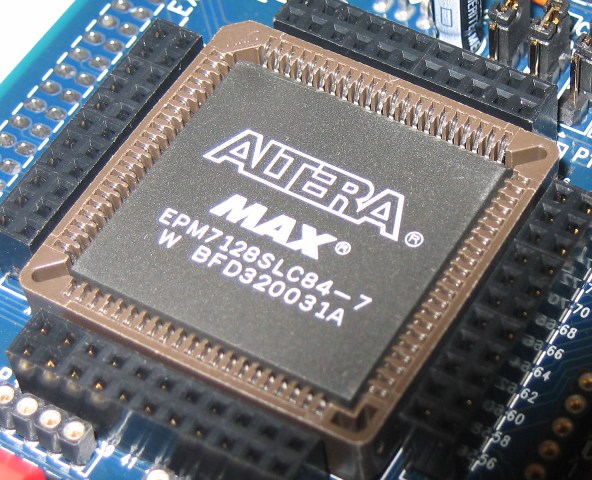

Kitas pavyzdys - „CPLD“ lustų šeimos MAX II firmos „Altera“ blokinė schema.

Ir tos pačios šeimos žetonų struktūrinis planas.

Tarpinės padangos makro ląstelėms priskiriamos naudojant mazgą, pavyzdžiui, platintoją anglų kalba. tai skamba kaip loginis paskirstytojas, parodytas žemiau esančioje diagramoje, taip pat rodo perjungimo matricą (visuotinis maršruto sudarymo baseinas), o išvestyje makroelementai (makroelementai) turi du grįžtamus ryšius.

Išoriniai mikroschemų išėjimai yra prijungti prie makroelementų išvesties per kitą bloką (matricą) - ORP (Output Routing Pool), atkreipkite dėmesį, kad per jį INPUT logika yra prijungta prie GRP, kaip parodyta toliau pateiktoje iliustracijoje.

Pastaba:

Kai kurie CPLD yra vadinamieji tiesioginiai įėjimai (Direct Input) - jie yra tiesiogiai prijungti prie elementų įėjimų, todėl sumažėja vėlavimai.

FPGA struktūra yra tokia:

-

L - logiškai konfigūruojamas blokas;

-

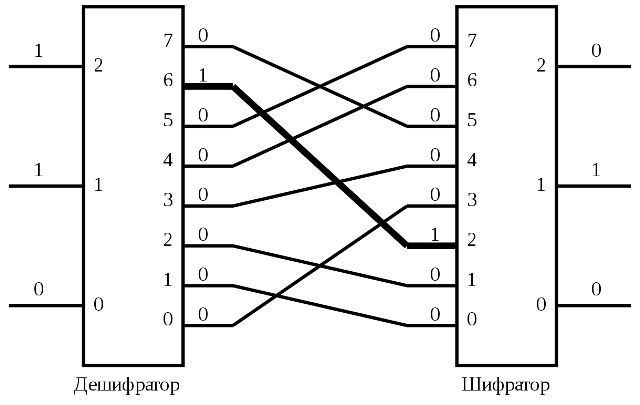

S (pakeitimo blokas) - pakeitimo blokas, jis gauna tam tikrą bitų skaičių per vieną judesį, konvertuoja pagal tam tikrą algoritmą ir išveda skirtingą bitų skaičių. Kitaip tariant, dekoderis, šifruotojas ir jungiklis.

-

C (jungčių blokas) - jungčių blokas.

S bloko schema:

Programavimas

HDL (aparatinės įrangos aprašymo kalba) - tai kalba, kuria programuojami FPGA. Populiarūs ir universalūs yra „Verilog HDL“ ir „VHDL“. Yra ir kitų kalbų, pavyzdžiui, specifinių gamintojams, pavyzdžiui, AHDL ALTERA gaminiams.

Grafinis programavimas yra prieinamas kūrėjams, kurie dirba su FPGA. Tai yra, jūs galite tiesiog nubrėžti logikos grandines arba derinti kodą su grafika. Pastarasis vadinamas moduliniu kūrimo metodu, kai nustatomi konkretūs moduliai, o viršutinis modulis, kuriame viskas derinama, užprogramuojamas grafiškai.

Populiarių gamintojų ir serijų pavyzdžiai

Rašymo metu garsiausi yra dviejų gamintojų produktai.

-

„Altera“ (įkurta 1983 m.);

-

„Xilinx“ (įkurta 1984 m.).

„Altera“ turi keletą pagrindinių programuojamos logikos serijų:

-

MAX, MAX II, MAX IIZ;

-

7000S;

-

3000A;

-

MAX V;

-

Ciklonas

-

Arija;

-

„Stratix“

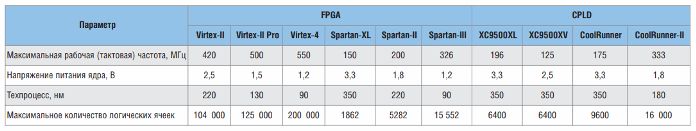

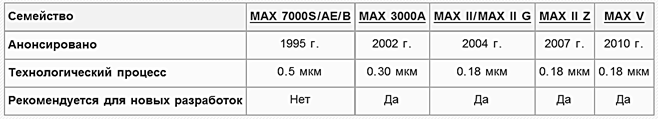

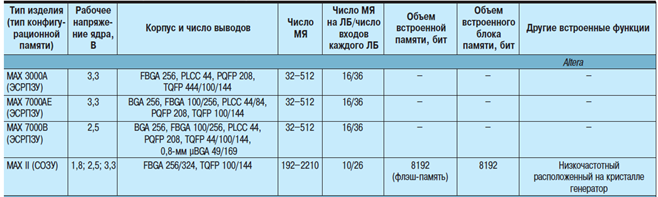

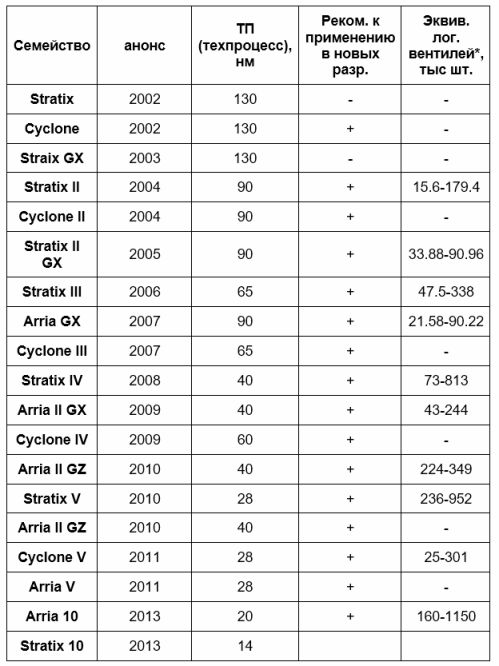

Apsvarstykime kiekvieną iš jų išsamiau. Žemiau esančiose lentelėse matote bendrą informaciją apie šeimos mikroschemus.

„Altera 3 CPLD CPLD“:

-

MAX yra mobiliųjų prietaisų CPLD, pasižyminti palyginti mažomis energijos sąnaudomis ir šilumos išsklaidymu. Atsižvelgiant į išleidimo sudėtingumą ir metus, išskiriamos šios modifikacijos:

-

„7000S“ yra pasenęs, jis buvo išleistas 1995 m.

-

„3000A“ - išleistas 2002 m., Pagamintas naudojant 300 nm technologiją. Susideda iš nedidelio skaičiaus makro ląstelių (32–512)

-

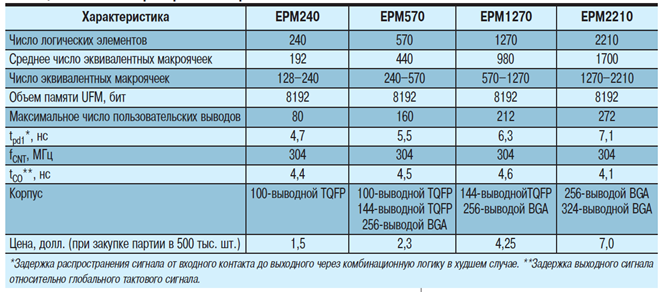

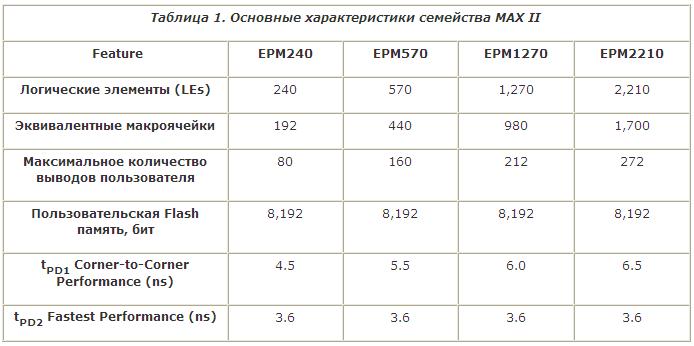

„MAX II“, išleistas 2004 m., Pagamintas naudojant 100 nm technologiją, susideda iš didesnio skaičiaus vienetų (240–210), veikiančių iki 304 MHz dažnio. Produktas pagamintas tais atvejais, kai TQFP 0.5 mill tipo yra 100 ar daugiau kojų.

-

„MAX IIZ - 2007“ pagrindinis bruožas yra mažesnis energijos suvartojimas - tai teigiamas teiginys, tačiau dažniai yra sumažinti iki 152 MHz. Šios mikroschemos maitinamos nuo 1,8 V.

-

MAX V - 2010 metai. Jis gaminamas pagal 180 nm technologiją, jame gali būti nuo 40 iki 2210 blokų ir veikti dažniais iki 152MHz arba 304MHz - tai priklauso nuo blokų skaičiaus.

FPGA:

-

Ciklonas yra biudžetinis FPGA tipo lustas. Yra penkios kartos, pažymėtos graikų skaičiais (atitinkamai nuo I iki V). Pirmoji karta buvo pradėta gaminti 2002 m., Pagaminta naudojant 180 nm technologiją, o penktoji karta buvo išleista 2011 m. Ir pagaminta naudojant 28 nm technologiją. Verta paminėti, kad visos kartos išlieka aktualios.

-

Arija - taip pat nurodykite vidutinės klasės FPGA.

-

„Stratix“ - galingi FPGA.

Žemiau yra „Altera FPGA“ programuojamų loginių suvestinių lentelės.

Visas pilnas stalas prie nuorodos:https://ltv.electricianexp.com/tablitsa.docx

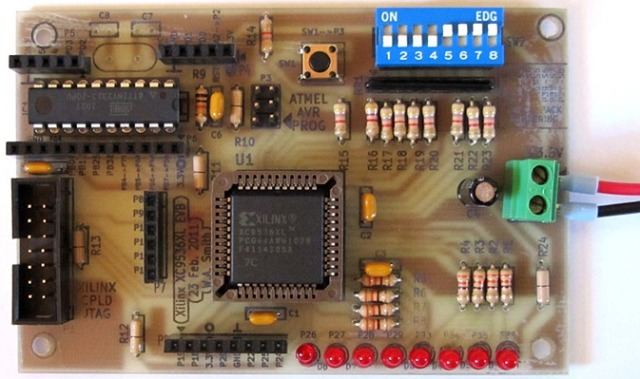

Gamintojas Xilinx CPLD pristatė serijomis:

-

XC9500XL iš 36-288 makro ląstelių. Jie veikia dažniais iki 178 MHz, o modeliai - su 288 makroelementais, esant 208 MHz dažniui. Tai atliekama kaip mažais atvejais su 44 kaiščiais (laidais) 0,8 mm atstumu vienas nuo kito - tokie atvejai laikomi lengvai litais. Taip pat galima įsigyti su 64 ir 100 kojų judesiais po 0,5 mm, taip pat su PLCC tipo korpusų modeliais.

-

„CoolRunner-II“ serija yra efektyvus energijos vartojimas, tačiau produktyvus CPLD. Funkcija maitinama 1,8 V įtampos, įėjimai ir išėjimai yra skirti veikti 1,5–3,3 V diapazone. Jie susideda iš 32–512 makro ląstelių ir yra gaminami naudojant 180 nm technologiją. Priklausomai nuo ląstelių skaičiaus, jie veikia 179–323 MHz dažnių diapazone, ir kuo mažesni langeliai, tuo dažnį jie tokiu atveju gali veikti. Jie aptinkami skirtingais atvejais, įskaitant lengvai litavimą, kaip ir aukščiau nagrinėtų serijų mikroschemose.

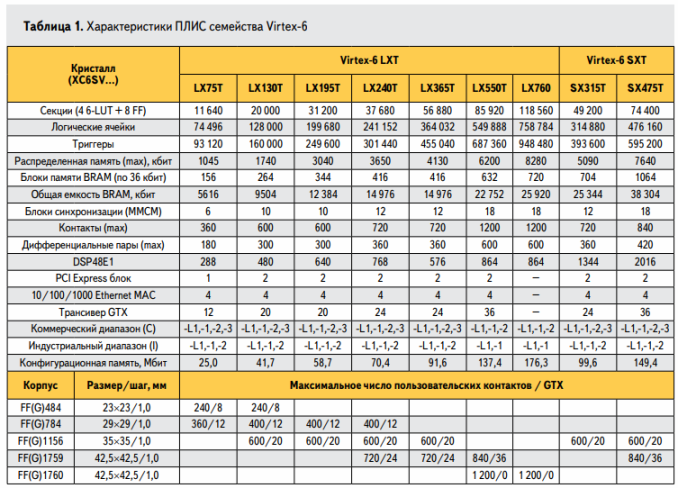

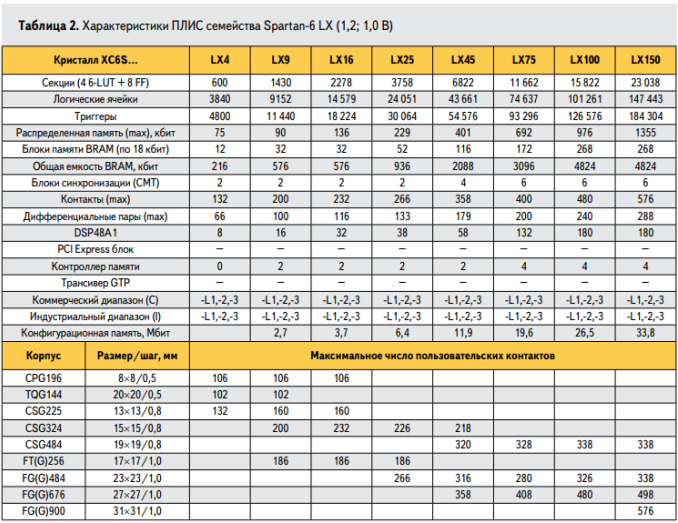

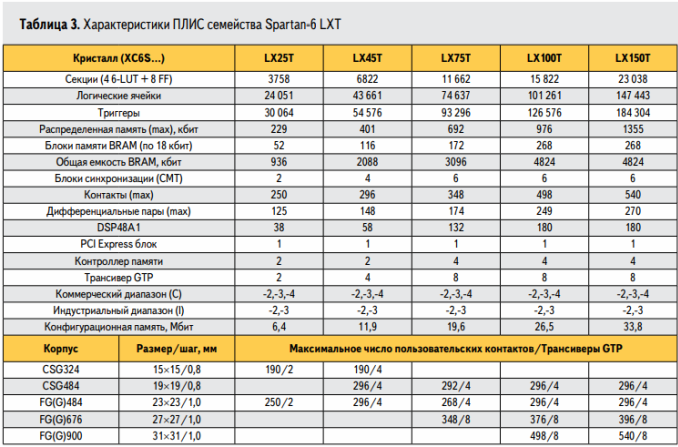

„Xilinx“ įmonė nepraėjo pro šalį ir FPGA:

-

„Spartan-6“ - susideda iš 6 įvestų loginių blokų, jų skaičius svyruoja nuo 3840–1447443 vienetų. Įdomu tuo, kad juose gali būti valdikliai, skirti keistis duomenimis, tokiais kaip DDR2, DDR3, PCI-EXPRESS, Ethernet 1Gbit, SerialATA ir kt.

-

„Vitrex-7“ serija yra sudėtinga, mikroschemose gali būti iki 2 000 000 loginių blokų ir 1 200 kontaktų.

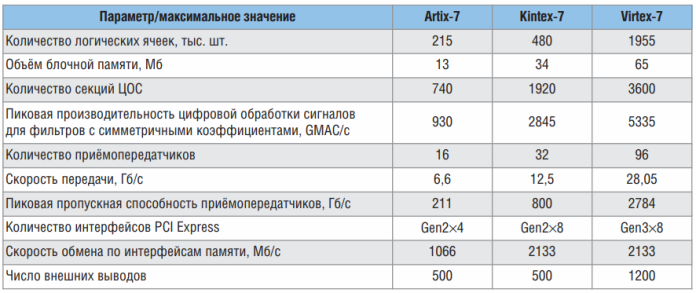

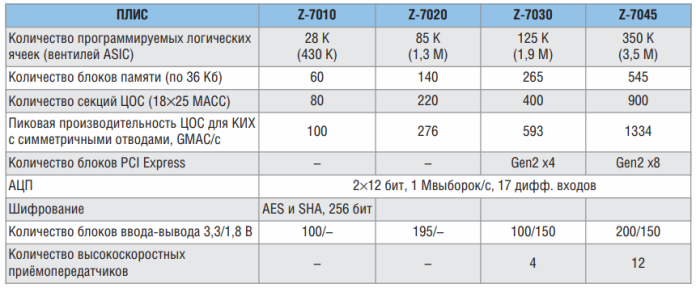

Žemiau rasite suvestines lenteles su CPLD ir FPGA specifikacijomis iš „Xilinx 6“ ir „7“ serijų, taip pat „Zynq-7000“.

Išvada

FPGA ir PPVM taip pat gamina kitos įmonės, tokios kaip „Lattice Semiconductor“ (2002 m. Pradėjo gaminti FPGA), „Actel“ ir jos žinomi mūsų svetainės skaitytojai. mikrovaldikliai ATMEL ir daugelis kitų. Pagal programuojamą logiką galima įdiegti daugybę prietaisų, įgyvendinti lygiagrečius, vienas nuo kito nepriklausomus skaičiavimus viename įrenginyje, tačiau namų projektams jų įsigijimas dažnai yra finansiškai nepagrįstas, tačiau gana pagrįstas gamybos mastu, kaip alternatyva pasirinktiniams integruotiems grandynams.

P.S.Žiūrėkite vaizdo įrašą, jame pamatysite „Nintendo“ žaidimų konsolės įdiegimo FPGA pavyzdį:

Taip pat žiūrėkite tinklalapyje bgv.electricianexp.com

: