Kategorie: Vybrané články » Praktická elektronika

Počet zobrazení: 12919

Komentáře k článku: 0

Čip 4046 (K564GG1) pro zařízení s rezonanční retencí - princip činnosti

Při vytváření výkonového elektronického zařízení s rezonanční retencí v LC obvodu je rezonanční řídicí obvod navržen pro synchronizaci přijatých kmitů s řídicími pulzy přicházejícími od řidiče.

Úkolem tohoto kontroléru je udržovat rezonanční oscilace v LC obvodu tím, že jej budí včas svými vlastními kmity. Aby toho bylo dosaženo, musí řídicí jednotka přijímat signál ze smyčky z obvodu obsahujícího data o aktuální frekvenci a fázi volných kmitů v ní, a poté, v závislosti na těchto datech, udržovat krok řidiče v synchronizaci s touto frekvencí a fází, poté rezonancí v okruhu se automaticky uloží.

K vytvoření takového ovladače je vhodný čip CD4046 nebo jeho domácí protějšek K564GG1. Pojďme se podívat na zařízení tohoto mikroobvodu, účel jeho závěrů a schéma zapojení namontovaných součástí, abychom pochopili, s čím se v případě potřeby zabýváte.

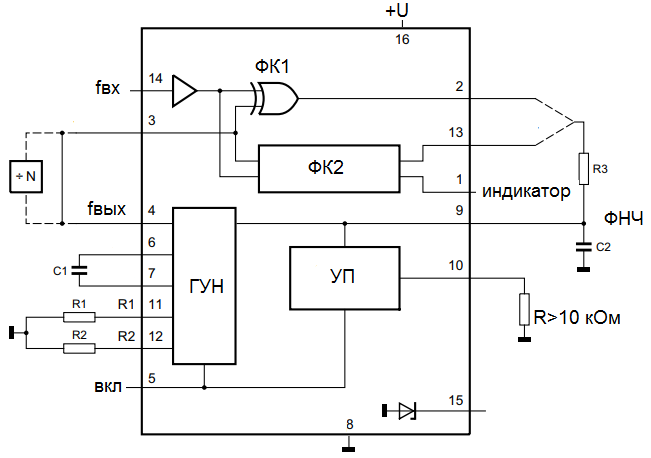

Tento čip umožňuje snadno organizovat obvod PLL - fázově uzamčená smyčka. K vytvoření PLL se používají tři nezbytné bloky, které jsou umístěny uvnitř mikroobvodu: VCO - napěťově řízený oscilátor, FC - fázový komparátor a LPF - dolní propust.

Vestavěný do mikroobvodu generuje VCO posloupnost pravoúhlých pulzů s 50% pokrytím, to znamená čistý meandr, jehož počáteční kmitočet závisí na parametrech dvou RC obvodů: R1C1 a R2C2 k němu připojených mimo mikroobvod, a amplituda je v tomto případě blízká napájecímu napětí mikroobvodu U +.

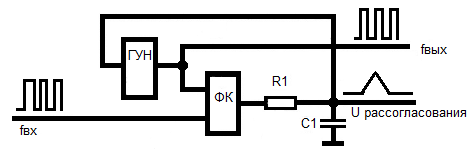

Princip činnosti PLL

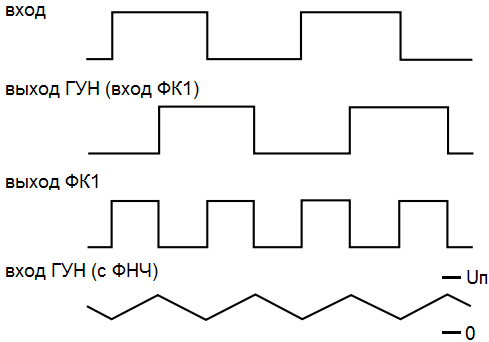

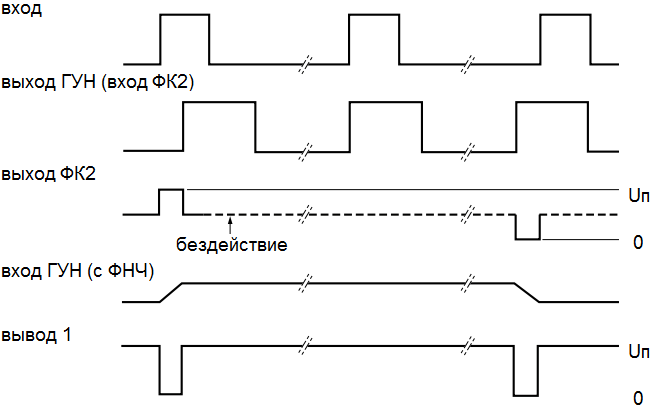

Externí vstupní signál fin je dodáván do mikroobvodu, ve skutečnosti, do jednoho ze vstupů fázového komparátoru FC (FC1 nebo FC2 - vývojář vybere) uvnitř něj. Meandr produkovaný VCO je současně přiváděn na druhý vstup FC. Výsledkem je, že na výstupu FC je získán obdélníkový signál, jehož trvání pulsu závisí na rozdílu mezi impulsy z VCO a externími impulsy v každém okamžiku.

Ve skutečnosti je doba trvání výstupních impulsů s FC úměrná fázovému rozdílu dvou porovnávaných signálů. Skutečnost je taková, že exkluzivní logický prvek OR je často používán jako FC, to znamená, že na výstupu FC bude vysoká úroveň napětí, pouze pokud bude rozdíl mezi signály, a pokud nebude žádný rozdíl, bude výstup z FC nízký úroveň napětí nebo neaktivní stav.

Z výstupu FC je signál veden do dolnoprůchodového filtru, což je jednoduchý RC obvod, na jehož kondenzátoru je získáno pulsující nesouladové napětí, přičemž úroveň zvlnění je úměrná rozdílu dvou signálů (z vnitřního VCO a dodávána do mikroobvodu z vnějšku), ve skutečnosti - fázový rozdíl .

Nesprávné napětí získané na kondenzátoru LPF je okamžitě přiváděno zpět na vstup VCO a v závislosti na jeho průměrné hodnotě bude frekvence VCO automaticky naladěna tak, aby se frekvence meandru na jeho výstupní meze blížila frekvenci vnějšího signálu přicházejícího z vnějšku mikroobvodu. Po dosažení takové situace bude průměrné napětí napříč kondenzátorem dolnoprůchodového filtru nejmenší - to je známkou maximální konvergence dvou signálů ve frekvenci a fázi. Když je tedy signál zachycen, bude ho nadále držet smyčka PLL.

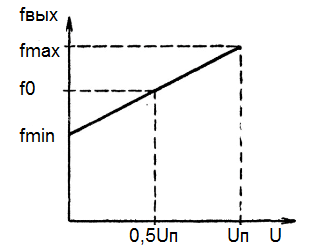

Meze reorganizace VCO

Jak jste již pochopili, frekvence VCO je schopna ladit v rámci určitého rozsahu automatického ladění. Tento rozsah je nastaven externími komponentami čipu. Reakční rychlost systému PLL je určena časovou konstantou LFF (hodnoty C2 a R3).Z tohoto důvodu byste měli přísně přistupovat k výběru připojených komponent čipu.

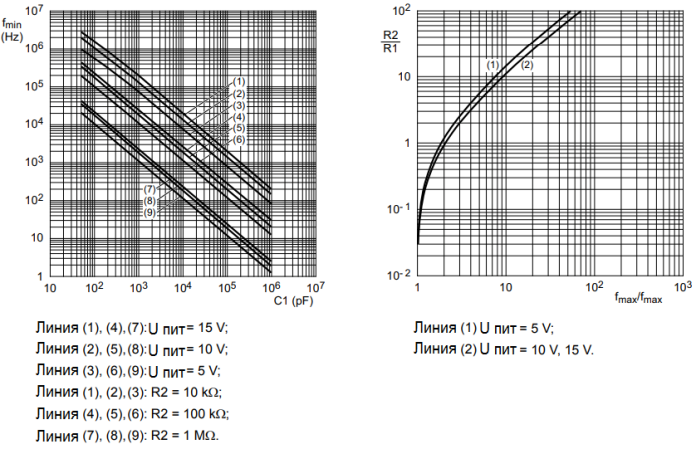

Napájecí napětí mikroobvodu, kondenzátoru C1, stejně jako rezistory R1 a R2, určují rozsah samočinného ladění kmitočtu VCO uvnitř mikroobvodu. Rezistor R2 ovlivňuje minimální frekvenci fmin VCO nad nulou. A poměr mezi hodnotami rezistorů R1 a R2 určuje poměr mezi maximální a minimální frekvencí - fmax / fmin, laditelný výstupní signál z VCO.

Čipové vstupy a výstupy

Závěr 4 - výstup signálu VCO, na něm v pracovním režimu meandr. Tento výstup lze použít k napájení signálu do dalších bloků navrženého zařízení.

Pin 5 je zodpovědný za zapnutí a vypnutí VCO. Pokud je na tento výstup přivedeno vysoké napětí, mikroobvod se vypne. Při použití nízkého napětí (při připojení kolíku 5 ke společnému vodiči) - mikroobvod bude fungovat v normálním režimu.

Závěry 6 a 7. K nim je připojen kondenzátor C1 - jedná se o kondenzátor kmitočtu VCO.

Závěr 8 - společný napájecí vodič čipu.

Rezistor R1 je mezi svorkou 11 a společným drátem. Rezistor R2 - mezi svorkou 12 a společným vodičem. Jedná se o odpory pro nastavení frekvence. Rezistor R3 dolního propusti - na pin 9 a pin 2 nebo 13 (rozdíl mezi nimi bude diskutován později), kondenzátor C2 dolního propusti je mezi pinem 9 a společným drátem.

Pin 10 je výstup zesilovače zesilovače. Napětí na něm během provozu mikroobvodu je nesouladové napětí dodávané do dolního propustného filtru. Závěr 10 je navržen tak, že nesouladové napětí může být v případě potřeby snadno izolováno bez posunutí kondenzátoru LPF. Za tímto účelem je dovoleno připojit odpor s odporem větším než 10 kOhm.

Závěr 15 - je to katoda vestavěné zenerovy diody se stabilizačním napětím 5,6 V (stabilizační napětí této zenerovy diody se může lišit v závislosti na výrobci čipu). Tato Zenerova dioda může být volitelně použita v napájecím obvodu čipu.

Závěr 16 - plus výkon čipu.

Vstupy a výstupy fázových komparátorů FC1 a FC2

Meandr z výstupu VCO je odebrán z terminálu 4 a přiváděn na terminál 3, připojený přes zesilovač-shaper ke vstupům fázových komparátorů FC1 a FC2. Pokud je to žádoucí, signál z VCO může být případně veden přes dělič kmitočtu.

Vstup 14 je signálový vstup a je do něj přiváděn vstupní signál, s nímž je nutné synchronizovat výstupní signál na výstupu VCO. V závislosti na povaze vstupního signálu si vývojář může vybrat, který fázový komparátor použít: FC1 nebo FC2, a připojit rezistor LPF k vybranému komparátoru (na pin 2 nebo 13). Fázový komparátor FC2 má indikátorový kolík 1, na kterém se objeví vysoké napětí, když jsou signály maximálně synchronizovány.

Zvláštností FC1 je to, že se jedná o jednoduchý exkluzivní logický prvek OR, a kvalita jeho činnosti závisí na parametrech dolního propustného filtru na jeho výstupu. Práce začíná střední frekvencí f0 = (fmax-fmin) / 2, je možné zachytit harmonické frekvence středové frekvence. Má vysokou hlučnost.

Zvláštností FC2 je to, že zpracovává pouze kladné rozdíly impulsů, které mu byly dodány, a proto nezáleží na pracovním cyklu impulsů. Práce začíná minimální frekvencí fmin, není možné zachytit harmonické kmitočty centrální frekvence. Má nízkou hlučnost. U dolního propustného filtru je vyžadován kondenzátor s nízkým svodovým proudem. FC2 je vhodnější pro použití v silových obvodech s LC rezonancí.

Výběr příloh

Jako dolní propust dolního propusti je nainstalován odpor R3 a kondenzátor C2. Aby PLL fungovala správně, musí být časová konstanta RC desetkrát větší než přibližná frekvence zachycení PLL.

Zpravidla je vývojová frekvence přibližně známa vývojáři, proto jsou zpočátku nastavena v rozsahu automatického ladění kmitočtu: fmin a fmax. První nomogram určuje, s ohledem na napájecí napětí mikroobvodu a požadované fmin, hodnoty R2 a C1.Poté se podle druhého nomogramu na základě požadovaného poměru fmax / fmin vybere R1. Je lepší poskytnout schopnost upravit odpory v obvodu.

Viz také na bgv.electricianexp.com

: